Une stratégie pour synthétiser des nanofeuilles métalliques en forme d’ailettes pour les transistors 2D

Crédit : Zhang et al.

L’intégration efficace de couches isolantes extrêmement minces avec des semi-conducteurs bidimensionnels (2D) pourrait permettre la fabrication de transistors 2D avec une capacité électrique comparable à celle du SiO2 avec des épaisseurs inférieures à 1 nm. Ces transistors pourraient, à leur tour, contribuer à améliorer les performances et à réduire la consommation d’énergie des appareils électroniques.

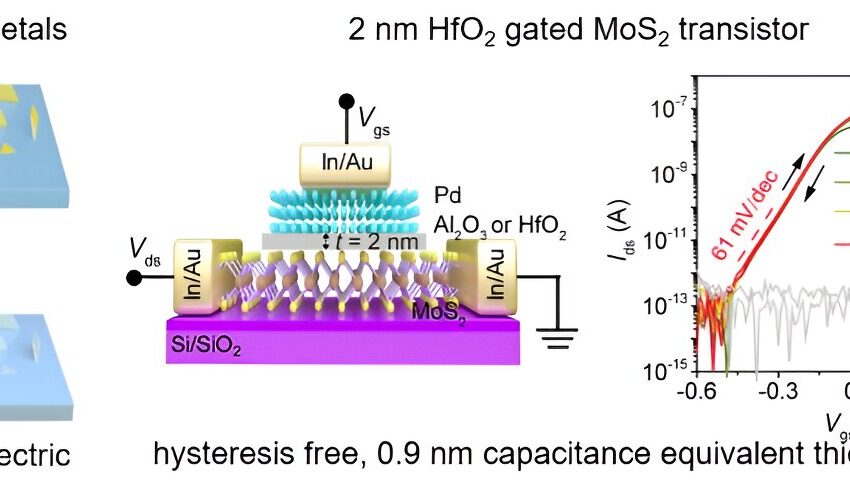

Des chercheurs de l’Université Nankai en Chine ont récemment présenté une nouvelle stratégie pour synthétiser des nanofeuilles métalliques monocristallines qui pourraient être facilement transférées sur des substrats 2D. Cette stratégie, décrite dans un article publié dans Électronique naturellea été utilisé avec succès pour déposer des diélectriques de 2 nm d’épaisseur à base d’Al2O3 ou HfO2 pour les transistors à grille supérieure hautement performants.

« Au tout début, notre objectif était de développer la stratégie de synthèse par dépôt chimique en phase vapeur (CVD) du Cu 2D2O, qui est un p« Semi-conducteur 2D à haute mobilité de type « 2D », a déclaré Jinxiong Wu, auteur correspondant de l’article, à Tech Xplore.

“Cependant, nous avons obtenu le métal élémentaire Cu en utilisant CuCl et Bi2O3 comme précurseurs de réaction. De plus, en changeant les types de chlorures métalliques, nous pouvons également obtenir d’autres métaux 2D, tels que Pd et Au.”

En examinant la littérature existante, Wu et ses collègues ont découvert que les métaux 2D à base de Pd et d’Au n’avaient pas encore été synthétisés par CVD, un procédé couramment utilisé pour produire des films ou des matériaux minces sur un substrat. Il est intéressant de noter qu’ils ont également réalisé que presque toutes les nanofeuilles métalliques 2D ont des surfaces atomiquement plates et peuvent être cultivées verticalement sur un substrat.

« Je me suis toujours demandé, ainsi qu’à mes étudiants, ce que nous pouvons faire avec ces connaissances », a déclaré Wu. « Juste au moment où nous étions sur le point d’abandonner le projet, la configuration du transistor à effet de champ à ailettes m’a inspiré.

« Si nous pouvons intégrer les métaux 2D développés verticalement avec des diélectriques déposés en couches atomiques (ALD) atomiquement minces, cela peut éviter le problème de compatibilité entre la technologie ALD et les semi-conducteurs 2D, ainsi que l’étape destructive du dépôt d’électrodes à grille supérieure sur des diélectriques ultra-minces, offrant ainsi une voie vers la fabrication de FET 2D avec une épaisseur équivalente à une capacité inférieure au nanomètre. »

Pour intégrer des nanofeuilles métalliques et des matériaux diélectriques, Wu et ses étudiants ont déposé directement des diélectriques atomiquement minces et plats, à savoir Al2O3 et HfO2sur des métaux 2D cultivés verticalement. Contrairement au sulfure de métal de transition 2D, le disulfure de molybdène (MoS2), qui est couramment utilisé comme semi-conducteur de canal dans les transistors, les métaux 2D ont une surface compatible avec les techniques ALD. Après la croissance ALD, la pile métal/oxyde peut être intégrée aux semi-conducteurs 2D à l’aide d’un processus en une seule étape qui forme une interface van der Waals.

L’étude récente de cette équipe de chercheurs a introduit une approche très prometteuse pour fabriquer des transistors 2D à base de métaux 2D et de diélectriques déposés par couches atomiques. Leur stratégie proposée implique l’utilisation de métaux 2D verticaux ultra-lisses pour permettre la croissance ALD de haute qualité de matériaux ultra-minces à haute teneur en carbone.k oxydes, ainsi que l’intégration ultérieure en une étape de van der Waal des piles métal/oxyde.

« Notre stratégie ne s’attaque pas seulement au problème d’incompatibilité entre la technologie ALD et les semi-conducteurs 2D, mais peut également éviter l’étape destructive du processus de dépôt d’électrode de grille supérieure sur les diélectriques ultra-minces, rendant ainsi possible le grand défi consistant à faire évoluer la valeur CET des FET 2D sans couche de germination jusqu’au sous-nanomètre », a déclaré Wu.

Dans le cadre de leur étude, les chercheurs ont utilisé leur stratégie CVD proposée pour créer des diélectriques de 2 nm d’épaisseur à base d’Al2O3 ou HfO2qu’ils ont ensuite utilisé pour fabriquer des transistors à grille supérieure. Lors des premiers tests, les transistors obtenus ont obtenu des résultats prometteurs, présentant des courants de fuite de 10−6Un cm−2des tensions de fonctionnement faibles de l’ordre de 0,45 V et une hystérésis inférieure à 1 mV.

« Nous croyons que la méthodologie développée par Bi2O3« La croissance CVD assistée par ordinateur est une avancée importante dans le domaine de la croissance CVD de matériaux 2D, car elle permet la synthèse de certains nouveaux matériaux 2D qui sont difficiles à synthétiser à l’aide de méthodes traditionnelles », a ajouté Wu. « Nous prévoyons maintenant de réaliser une fabrication à l’échelle de la tranche de transistors 2D sans hystérésis avec une épaisseur équivalente de capacité inférieure à 1 nm. »

Plus d’information:

Lei Zhang et al., Nanofeuilles métalliques cultivées verticalement intégrées à des diélectriques déposés par couches atomiques pour transistors avec des épaisseurs équivalentes à une capacité subnanométrique, Électronique naturelle (2024). DOI : 10.1038/s41928-024-01202-3.

© 2024 Réseau Science X

Citation:Une stratégie pour synthétiser des nanofeuilles métalliques en forme d’ailettes pour les transistors 2D (2024, 31 juillet) récupéré le 31 juillet 2024 à partir de

Ce document est soumis au droit d’auteur. En dehors de toute utilisation équitable à des fins d’étude ou de recherche privée, aucune partie ne peut être reproduite sans autorisation écrite. Le contenu est fourni à titre d’information uniquement.