Un nouveau framework conçoit des transistors 3D évolutifs basés sur des semi-conducteurs 2D

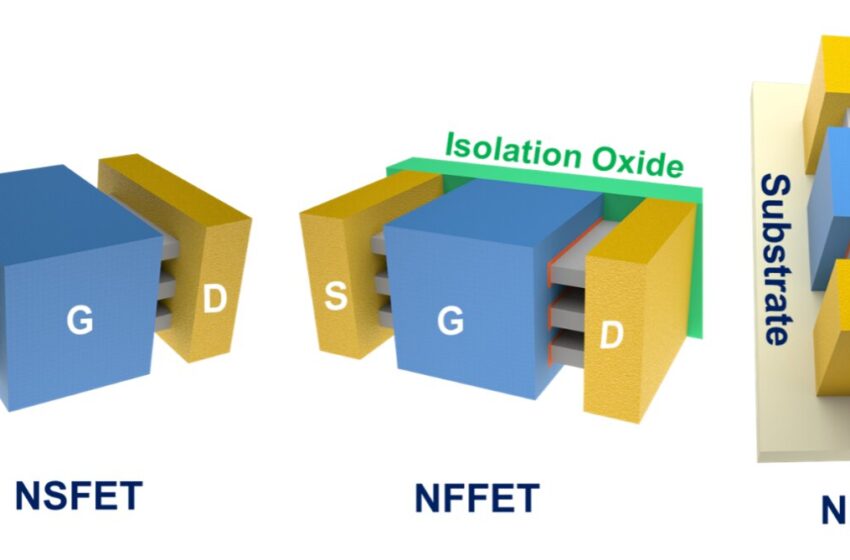

(De gauche à droite) L’œuvre représente les futurs transistors à effet de champ (FET) CMOS tridimensionnels (3D) sous la forme d’une nano-feuille (NSFET), d’une nano-fourchette (NFFET) et d’une nano-plaque (NPFET). , le tout rendu possible de manière unique par des semi-conducteurs en couches bidimensionnelles (2D) atomiquement minces. Crédit : Pal et al., Électronique naturelle2024.

L’électronique conventionnelle basée sur le silicium approche de ses limites en termes de performances et d’évolutivité. Ces dernières années, les ingénieurs ont donc tenté d’introduire des conceptions alternatives qui pourraient contribuer à réduire la taille des composants électroniques tout en améliorant leur vitesse et leur efficacité énergétique.

Des chercheurs de l’Université de Californie à Santa Barbara ont conçu un nouveau cadre qui pourrait contribuer à cette quête, en permettant la fabrication de transistors à effet de champ (FET) tridimensionnels (3D) évolutifs basés sur des semi-conducteurs en couches bidimensionnels (2D). L’approche proposée, décrite dans Électronique naturellereprésente les facteurs clés qui peuvent influencer les performances de ces transistors, notamment les effets de contact Schottky et la capacité inclusive.

“Notre groupe de recherche a été l’un des premiers contributeurs à souligner l’importance d’une architecture multi-portes pour obtenir des FET réalistes inférieurs à 10 nm, même avec des canaux atomiquement fins basés sur des semi-conducteurs 2D”, a déclaré Kaustav Banerjee, auteur principal de l’article. dans une interview avec Tech Xplore.

“Cette perspective a été explorée plus en détail dans nos récents travaux sur les futurs transistors, où nous avons collaboré avec des experts de premier plan de l’industrie des semi-conducteurs pour mettre en évidence le potentiel des transistors tridimensionnels.”

L’objectif principal des travaux récents de Banerjee et de ses collègues était de démontrer le potentiel des matériaux en couches 2D atomiquement minces pour la fabrication de FET 3D de nouvelle génération avec diverses architectures. En outre, les chercheurs espéraient mieux comprendre quels matériaux, architectures et conceptions seraient optimaux pour ces transistors.

Au cours de leur étude, ils ont découvert que les matériaux 2D peuvent également être conçus de manière unique pour créer une toute nouvelle architecture de transistor, qu’ils ont baptisée FET à nano-plaques (NPFET). Cette architecture pourrait présenter des performances améliorées et une plus grande densité d’intégration.

Architecture NPFET 2D. Crédit: Électronique naturelle (2024). DOI : 10.1038/s41928-024-01289-8

“Le cadre proposé pour la conception de transistors 3D à l’échelle implique l’utilisation d’un formalisme de transport quantique pour simuler le transport de porteurs, à l’aide d’un outil de conception assistée par ordinateur (TCAD) disponible dans le commerce appelé QTX”, a expliqué Banerjee. “Cet outil exploite le cadre de fonctions de Green hors équilibre (NEGF), l’une des approches de transport quantique les plus puissantes.”

Pour différentes variantes de la fonction NEGF, les chercheurs ont utilisé une approche efficace basée sur la masse. Cette méthode s’est avérée efficace et précise sur le plan informatique, tout en tenant également compte des effets de non-parabolisme des bandes d’énergie, des vallées satellites et de la largeur d’énergie finie de ces vallées.

“Ces paramètres d’entrée ont été calculés avec des simulations de la théorie fonctionnelle de la densité (DFT), une méthode ab-initio, puis importés dans QTX”, a déclaré Banerjee. “Nous avons également pris en compte l’effet d’une résistance de contact non idéale et de la mobilité des porteurs pour effectuer des simulations plus approfondies.”

Les résultats des simulations réalisées par les chercheurs suggèrent que les FET 3D à base de semi-conducteurs 2D peuvent atteindre des performances supérieures à celles des FET à base de silicium. La longueur du canal de ces FET 3D basés sur des matériaux 2D a été réduite à environ 7 nm ou moins et le matériau qui a généré les gains les plus importants était le WS.2.

“L’augmentation du courant de commande, associée à la capacité réduite du dispositif en raison de la finesse du semi-conducteur 2D par rapport au silicium, améliore le produit de retard d’énergie (EDP) global des circuits conçus avec des transistors à base de semi-conducteurs 2D”, a déclaré Banerjee. “De plus, nous avons fourni un plan complet pour la conception de FET 3D basés sur des semi-conducteurs 2D afin de prendre en charge la future mise à l’échelle CMOS.”

Pour mettre à l’échelle les transistors, la nouvelle architecture NPFET introduite par cette équipe de recherche exploite la finesse et l’empilement vertical des semi-conducteurs 2D. Par rapport aux architectures 3D-FET comparables introduites dans des études précédentes, cette architecture pourrait offrir des avantages importants en termes de densité d’intégration et de performances.

“Nos futurs efforts de recherche se concentreront sur une collaboration étroite avec des partenaires industriels pour accélérer l’intégration de ces matériaux et conceptions dans les processus CMOS traditionnels”, a ajouté Banerjee. “De plus, nous visons à améliorer nos simulations en incorporant une gamme plus large d’effets non idéaux, tels que la diffusion des défauts et l’auto-échauffement. Cela fournira des informations plus approfondies et un soutien aux chercheurs expérimentaux dans ce domaine.”

Plus d’informations :

Arnab Pal et al, Transistors tridimensionnels avec semi-conducteurs bidimensionnels pour une future mise à l’échelle CMOS, Électronique naturelle (2024). DOI : 10.1038/s41928-024-01289-8.

© 2025 Réseau Science X

Citation: Un nouveau framework conçoit des transistors 3D évolutifs basés sur des semi-conducteurs 2D (14 janvier 2025) récupéré le 14 janvier 2025 sur

Ce document est soumis au droit d’auteur. En dehors de toute utilisation équitable à des fins d’étude ou de recherche privée, aucune partie ne peut être reproduite sans autorisation écrite. Le contenu est fourni à titre informatif uniquement.